Research Topics

SMT-Based Model Checking for Signal Temporal Logic

This research focuses on developing a formal foundation and verification technique for signal temporal logic (STL), which specifies properties of continuous signals in hybrid systems. The goal is to enable robust bounded model checking of general STL properties, with correctness guarantees up to given bounds.

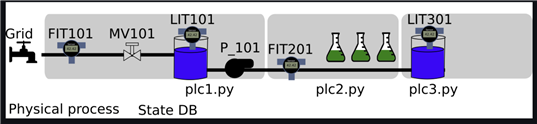

Formal Semantics and Analysis of PLC Systems

This research focuses on defining the behavior of the whole PLC behavior including the PLC ST, multitask, external environment, and communication features.

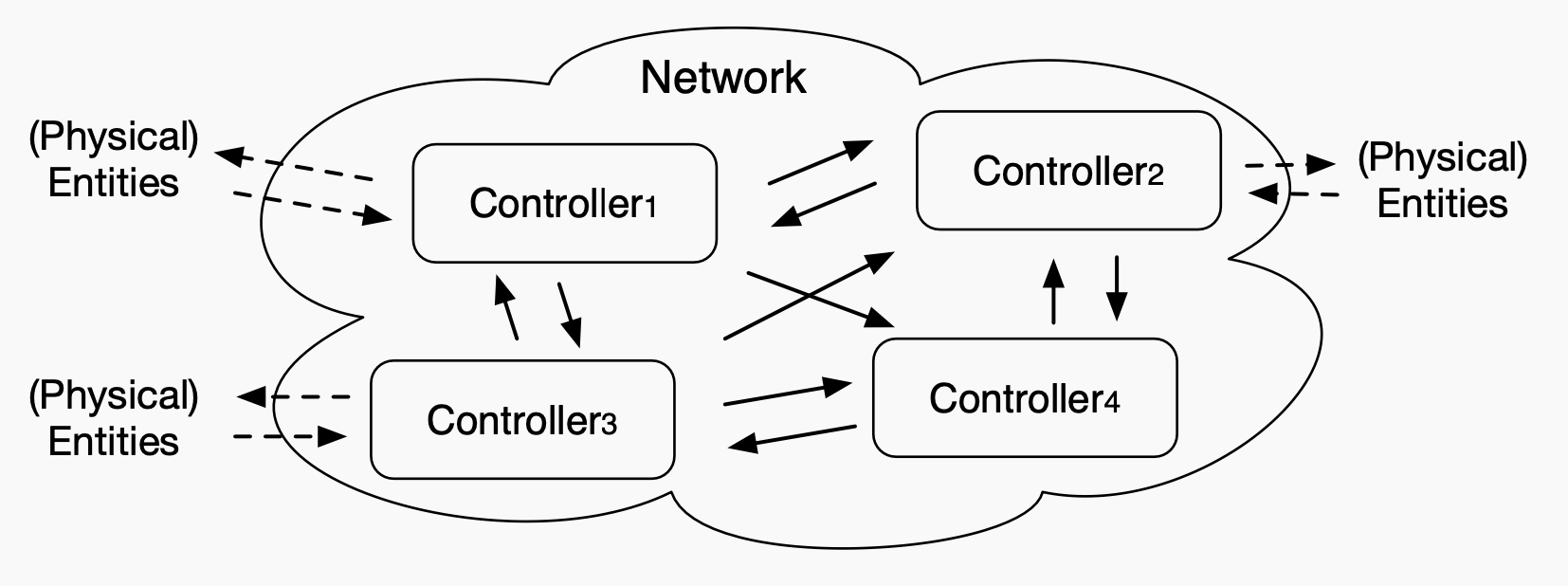

MR-HybridSynchAADL: Formal Modeling and Analysis of Multirate CPSs

We define the MR-HybridSynchAADL modeling language and verification tool for hierarchical multirate CPSs with advanced control programs, continuous behaviors, and imprecise local clocks.

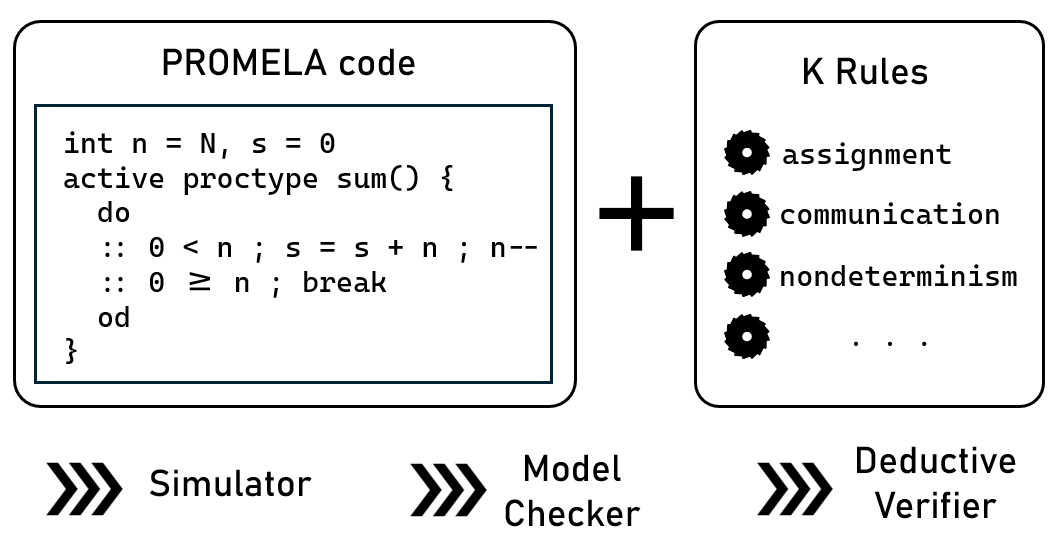

A Formal Executable Semantics of Promela for Deductive Verification

This project defines formal semantics of Promela using the K-Framework, with a support for deductive verification

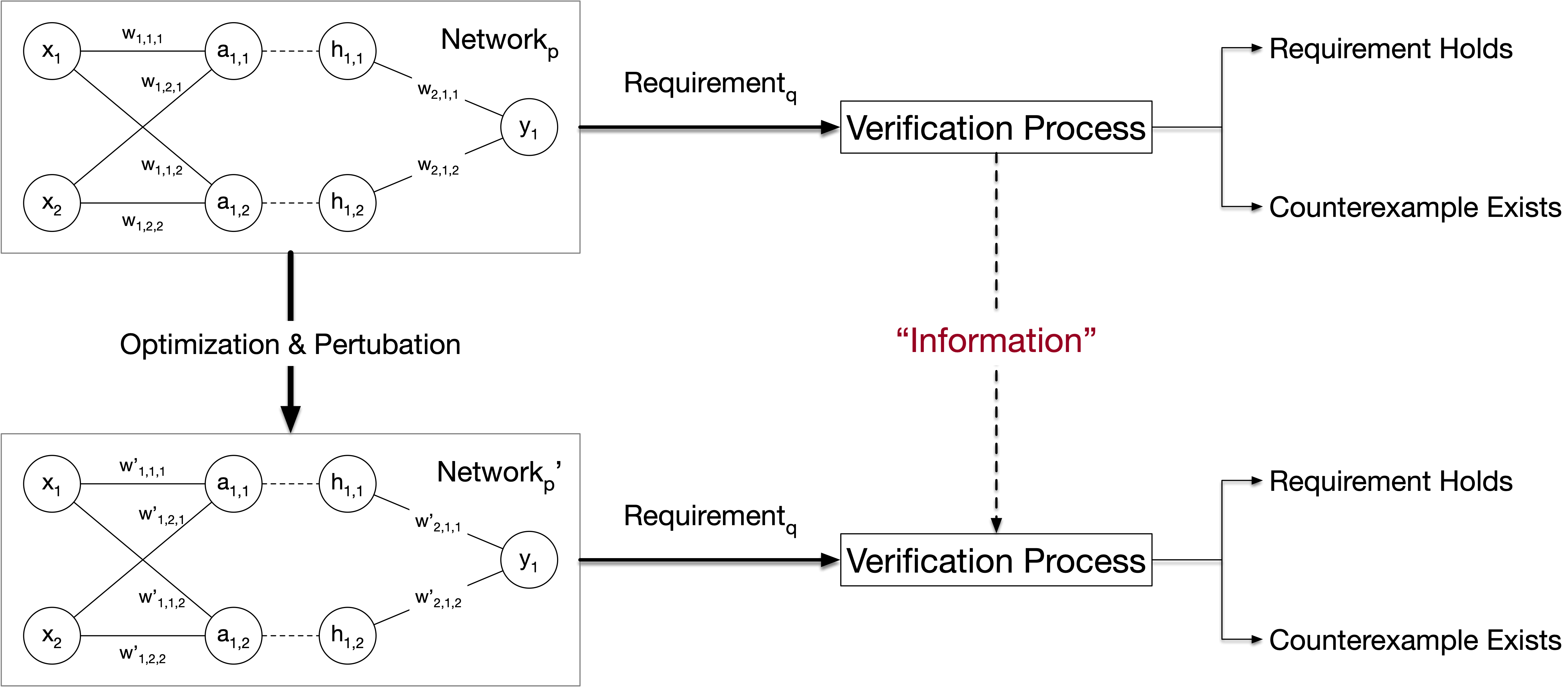

Utilization of Activation Property for Efficient Incremental Neural Network Verification

In this research, we propose an "Activation Property", a form of information that can be extracted from previous verification processes, and develop a framework that leverages this for efficient incremental verification of neural networks. The proposed framework allows SOTA Branch-and-Bound(BaB)-based verifiers to support incremental verification with minimal modifications while improving verification performance.

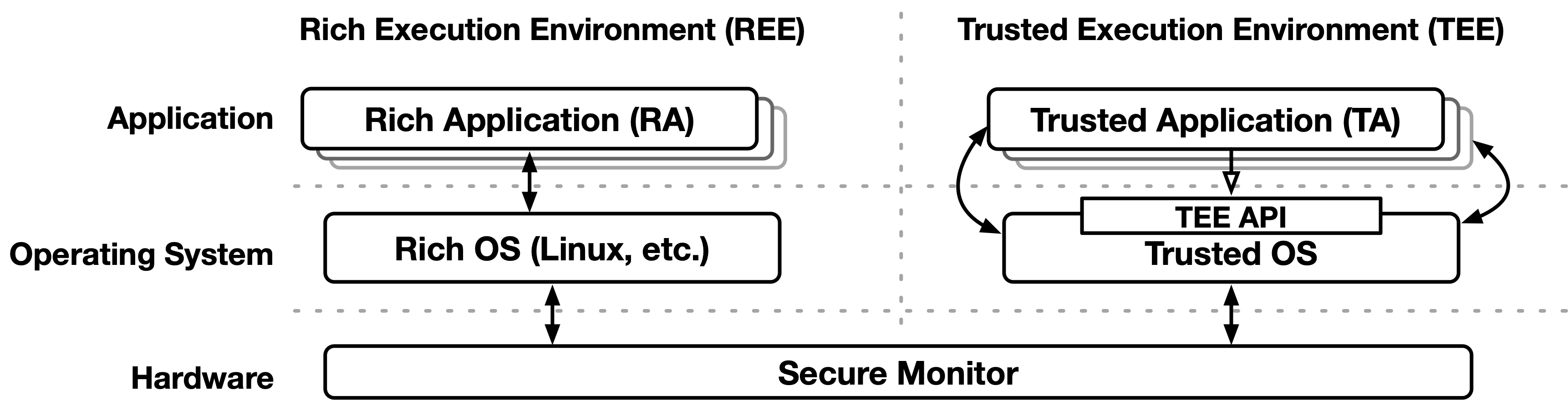

Formal Specification of Trusted Execution Environment APIs

This research focuses on presenting a formal specifcation of TEE APIs by leveraging Maude, to support formal analysis and verification of TEE applications.

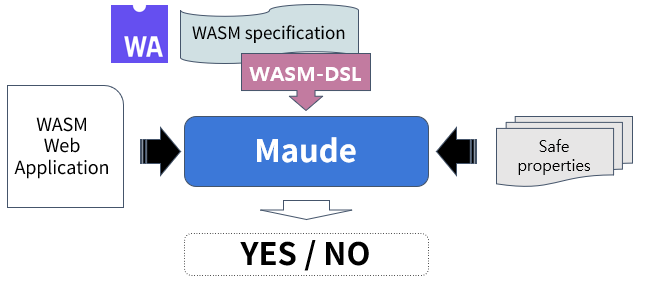

Model Checking of Webassembly Programs

WebAssembly (WASM) is a binary standard designed to execute high-performance programs on web browsers. Various verification techniques have been applied to WASM programs. In this study, we propose a model checking technique for WebAssembly programs using a rewriting logic-based Maude framework, aimed at verifying security properties related to concurrency and parallelism that have been challenging for existing methods.

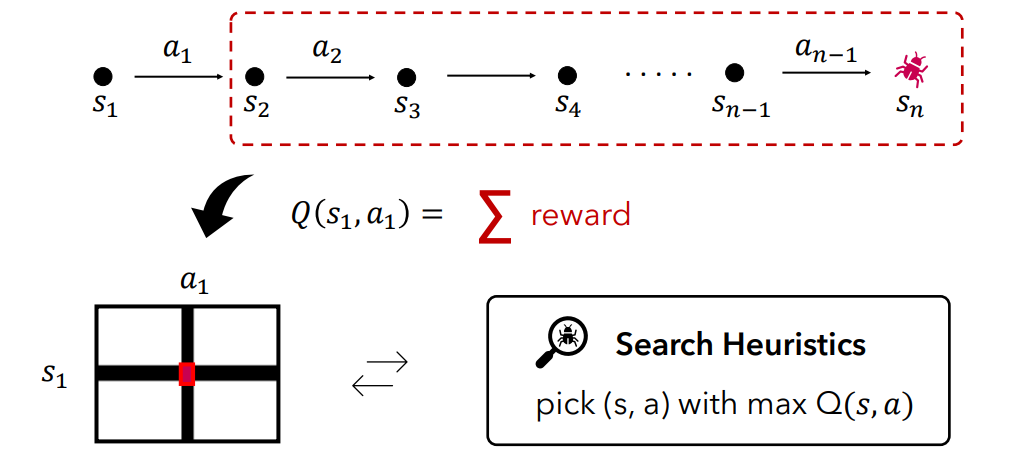

RL-based Heuristics Learning for Model Checking

This project leverages reinforcement learning to automatically learn search heuristics that improve the efficiency of model checking by guiding the exploration toward error states.

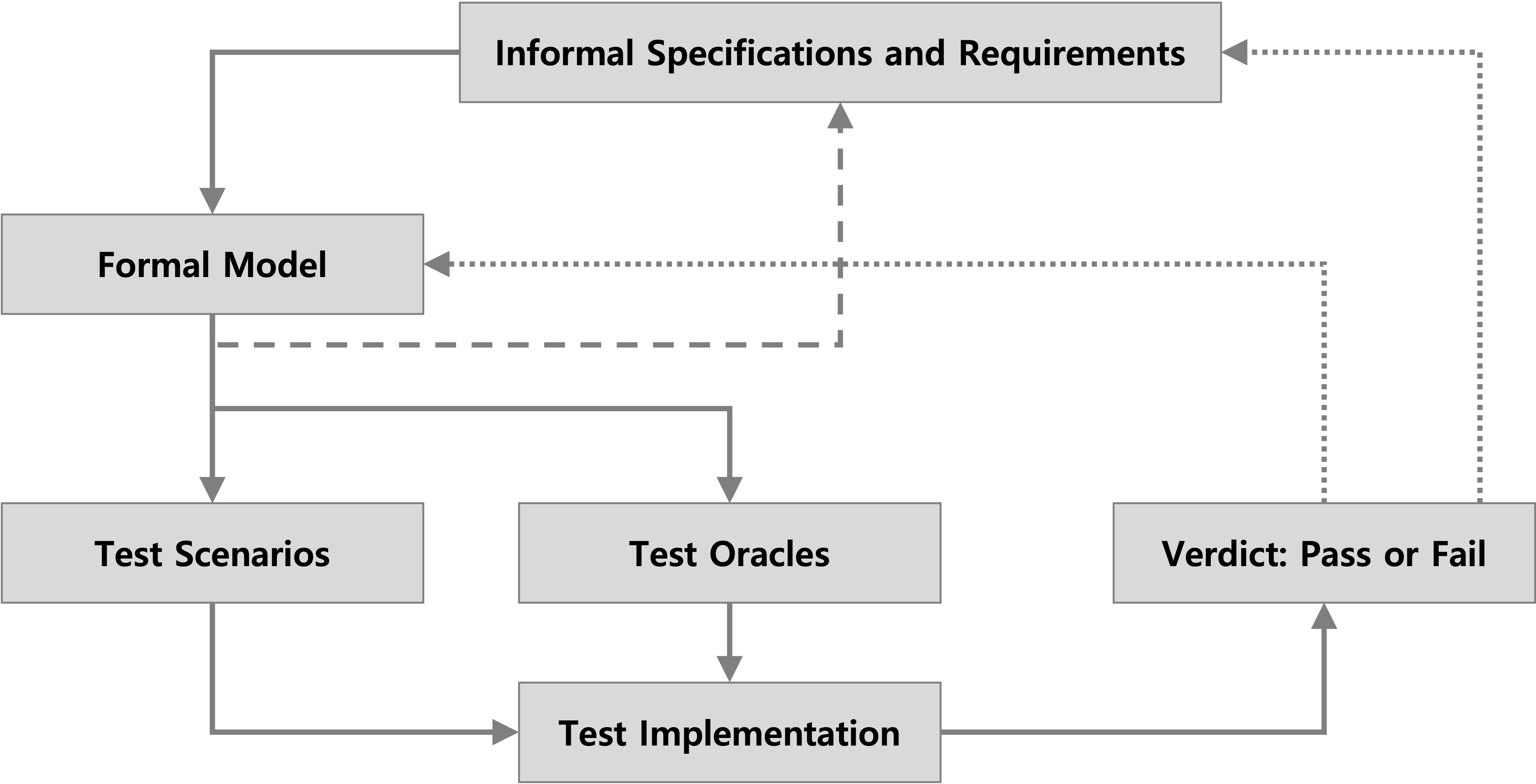

TLS Model-based Testing using Maude

We use model-based testing approach to test TLS libraries using Maude. By using Maude, we can generate more various and complicated test scenario automatically. We build an automated tool to test several TLS libraries.

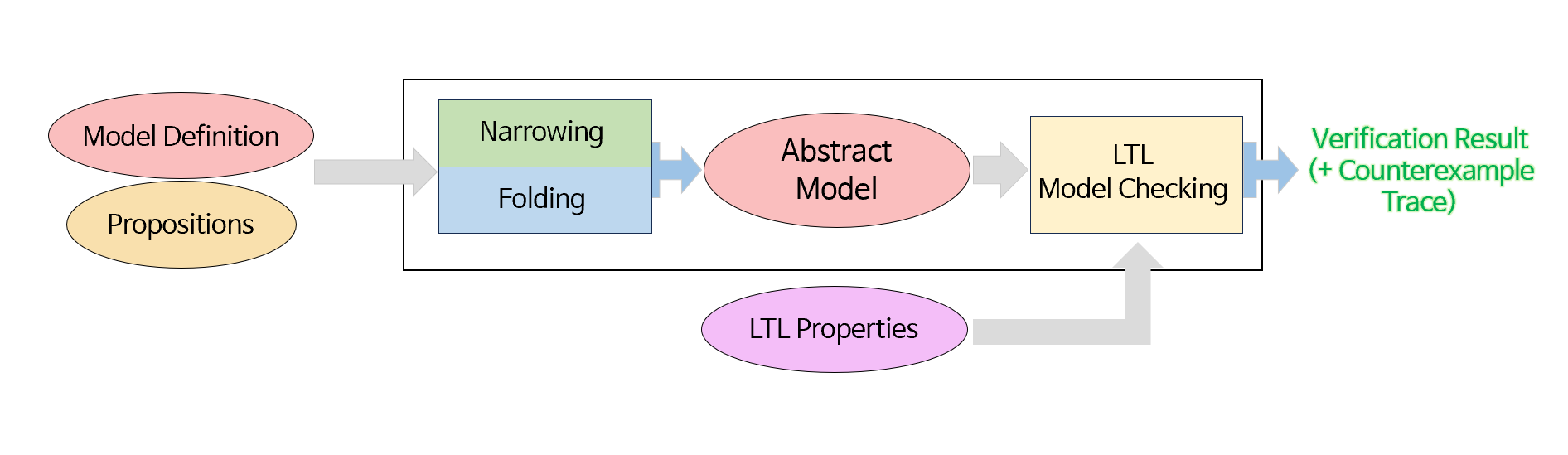

Model Checking of Infinite-State Systems using Narrowing

This research extends the Logical Model Checker (LMC) to verify a broader class of infinite-state systems by introducing a novel framework for constraint-based symbolic analysis and sound state-space reduction.

A Framework for Maude-SMT Integration

This research focuses on extending rewriting modulo SMT to support efficient and customizable symbolic analysis of infinite-state systems. The goal is to overcome the limitations of the existing Maude-SMT interface by enabling satisfying assignment generation, formula simplification, folding-based state-space reduction, and broader theory support including uninterpreted functions.

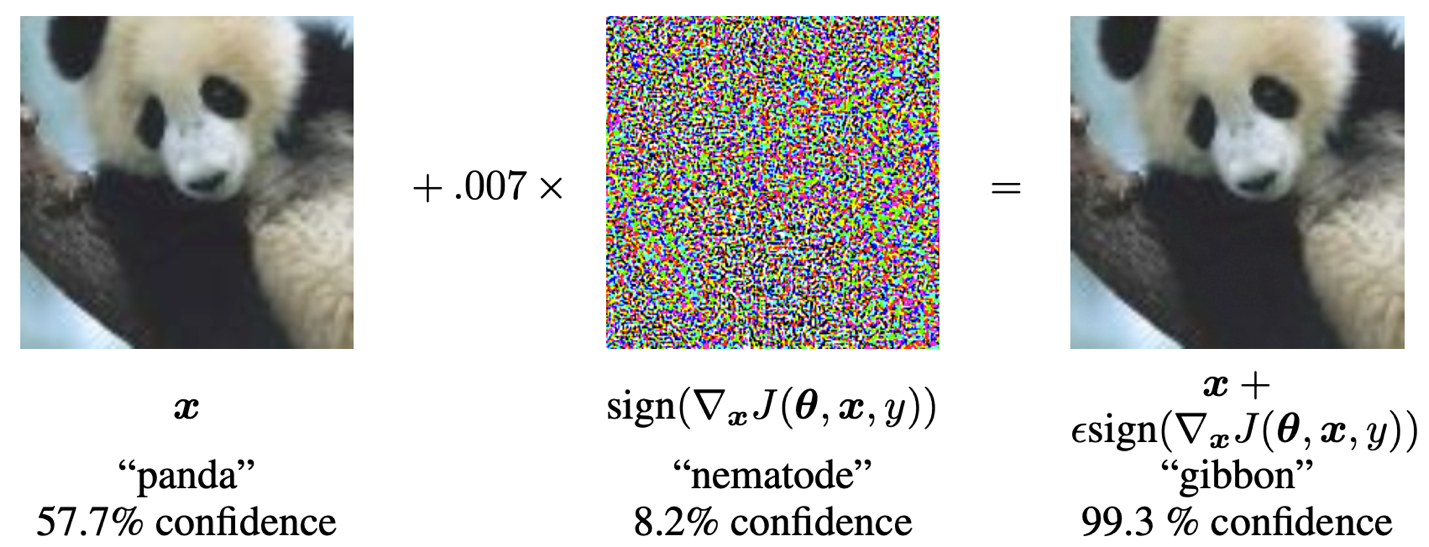

Layered Abstraction Technique for Effective Formal Verification of Deep Neural Networks

In this research, we propose a new technique, called layered abstraction, for non-linear activation functions, such as ReLU and Tanh, and the verification algorithm based on that. We have implemented our method by extending the existing SMT-based methods.